Con el fin de facilitar la comunicación entre circuitos en controles industriales, equipos de consumo y muchos otros tipos de aplicaciones, La Philips lanzó en 1992 un nuevo tipo de bus que permitía el uso de dos cables para el intercambio eficiente de información. El bus, llamado Inter IC o l2C, permite el uso de una gran variedad de componentes estandarizados, que pueden intercambiar datos de forma sencilla y eficiente.

Tal fue el éxito de este bus que en poco tiempo se convirtió en un estándar mundial, uno de los favoritos para aplicaciones que implican todo tipo de intercambio de datos entre circuitos utilizando cables trenzados. Este éxito llevó a la aparición de la versión 2.0 en 1998. Qué es I2C y cómo funciona, es lo que veremos en este artículo de 2001.

La idea básica de utilizar el bus I2C es permitir una fácil integración en los componentes de la interfaz, que pueden trabajar directamente con sus señales simplificando así la comunicación con otros componentes de la misma familia.

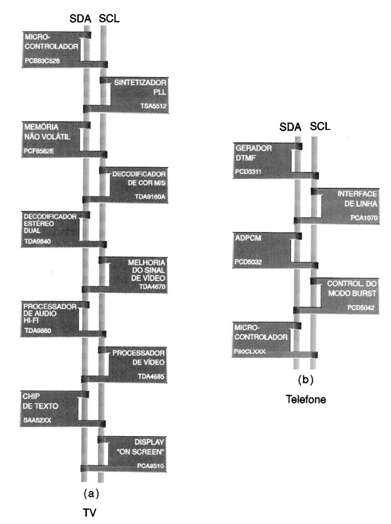

Para cuando La Philips lanzó este bus, más de 150 circuitos integrados ICMOS ya eran compatibles con él. Vea la figura 1.

Para que los circuitos se comuniquen eficientemente, dentro de la idea básica del bus I2C se predijo que debían presentar las siguientes características básicas:

Emplear sólo dos cables: una serie data line (SDA) y una serie de clock line (SCL).Cada dispositivo que fuera conectado al bus debería ser redireccionado por software con una sola dirección, y relaciones simples maestro/esclavo

deberían estar disponibles todo el tiempo. En el tipo final, se utilizaron 10 bits para este direccionamiento.

Se deben proporcionar recursos para detectar la colisión de datos de modo que no haya daños en los datos transferidos en caso de transmisión simultánea. Las velocidades de transferencia de 100 kbits/s se utilizarían inicialmente en modo estándar o 400 kbit/s en modo rápido. Posteriormente, se omitió el modo de baja velocidad.

Se deben proporcionar circuitos de rechazo transitorios y picos en chip para preservar la integridad de los datos. El número de Cls conectados al mismo bus estaría limitado sólo por la capacitancia máxima del bus, de 400 pF.

La adopción de esta norma podría facilitar en gran medida el proyecto de equipos que necesitan comunicarse con otros de manera sencilla y eficiente, ya que no se requerirían interfaces adicionales. Más que eso, los componentes de todos los tipos podrían incorporar los circuitos de interfaz, lo que significa que para interconectarlos sería suficiente utilizar un par trenzado sin la necesidad de circuitos de interfaz adicionales.

En la figura 2 tenemos ejemplos de la aplicación de este bus a un televisor altamente integrado para la transferencia de datos entre etapas.

Otra aplicación muy atractiva es el uso del PC como alternativa al puerto RS-232 en la conexión de periféricos. Se han mantenido las ideas básicas de las aplicaciones y la versatilidad de uso del bus I2C, pero con su adopción como estándar mundial con licencia para su empleo en más de 50 empresas, algunas mejoras han aparecido en la versión 2.0, tales como:

• Se ha añadido el modo de alta velocidad (modo Hs) que permite la transferencia de datos a una velocidad de hasta 3,4 Mbits/s. Lo interesante es que tanto los dispositivos rápidos como los estándares pueden funcionar en la misma línea al mismo tiempo.

• El bajo nivel y la histéresis de los dispositivos con una tensión de alimentación de 2 V o menos se han adaptado para satisfacer los requisitos de los niveles de ruido para seguir siendo compatibles con los dispositivos de mayor la tensión de alimentación.

• Se omitió el requisito de 0,6 V bajo 6 mA para las etapas de salida de los dispositivos operativos en modo rápido.

• Los niveles de entrada fijos para los nuevos dispositivos han sido reemplazados por niveles de la tensión relacionados con el bus.

EL CONCEPTO

Los buses I2C aceptan cualquier proceso de fabricación Cls (NMOS, CMOS, Bipolar, etc.), lo que permite que los dispositivos de cualquier tecnología tengan los circuitos de estos bus encarnados, y que puedan comunicarse sin conflictos.

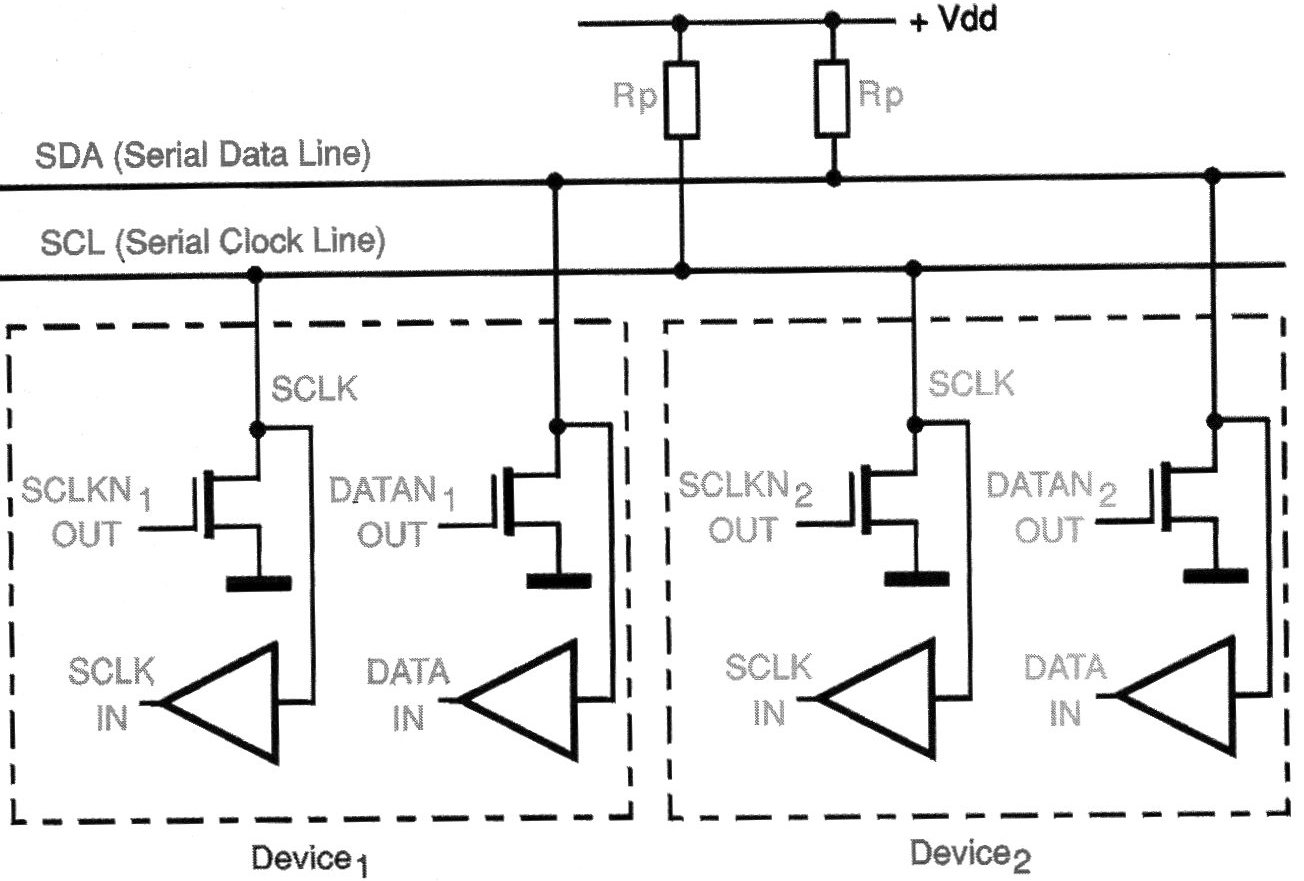

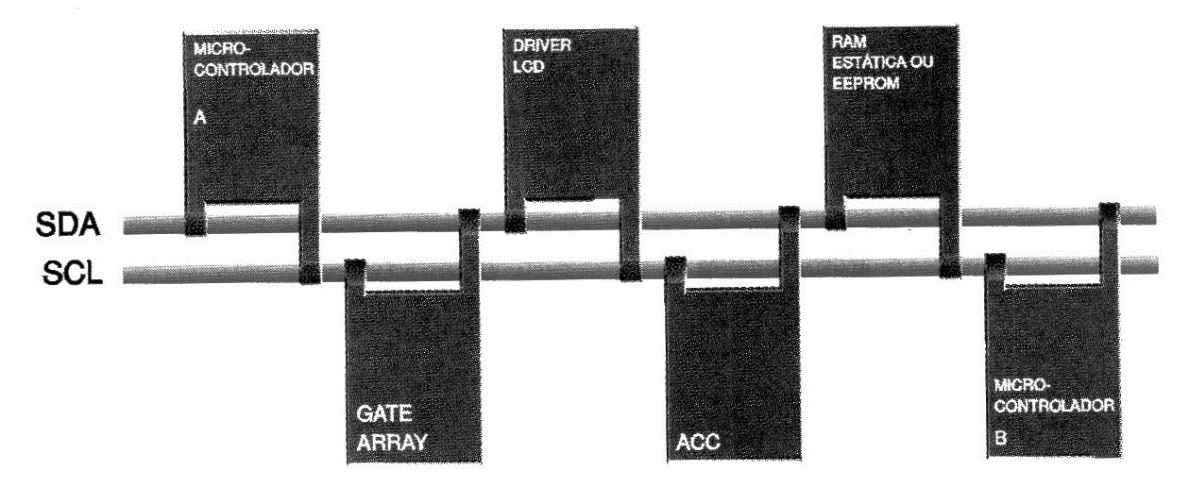

Dos hilos de datos (datos serie SDA y clock serie SCL) cargan la información entre los dispositivos conectados al bus, tal y como se muestra en la figura 3.

Cada dispositivo de bus es reconocido por una sola dirección, incluso si se trata de un microcontrolador, LCD, memoria o interfaz de teclado, y puede funcionar como un receptor o transmisor de datos dependiendo de sus fu

nciones.

Por supuesto, en el caso más simple que sería de un LCD, sólo tenemos un receptor que recibe los datos que deben presentar desde un transmisor, mientras que, en otros como un teclado, por ejemplo, puede recibir y enviar datos, ya que necesita comunicar a un periférico la tecla pulsada y recibir información en el momento en que se libera o que se espera que se active una determinada tecla.

Los dispositivos conectados al bus pueden tener varias clasificaciones, como maestro (MASTER) o esclavos (SLAVE), y algunos otros según la siguiente tabla:

Los dispositivos del Bus FC

Contrato Descripción

Transmisor Dispositivo que envía

dados al bus

Receptor Dispositivo que recibe Arbitraje Procedimiento que

dados del bus asegura que, si mas

Maestro Dispositivo que inicia de un maestro tentaran

una transferencia y al mismo tiempo

genera señales de clock controlar el bus,

y también termina una solamente uno es atendido

transferencia de datos y sus datos no son

Esclavo Dispositivo enviado afectados

Por el maestro Sincronización Procedimiento que

Multímetro más de un maestro sincroniza las señales

pueden tomar el control de clock de dos o

del bus al más dispositivos

mismo tiempo, sin

perder datos

El bus I2C es un multímetro. Esto significa que se puede conectar más de un dispositivo de control. En la figura 4 tenemos un ejemplo donde esto puede ocurrir.

Mientras que el microcontrolador 1 envía señales al driver LCD, el microcontrolador 2 intercambia información con el microcontrolador 3 utilizando el mismo bus.

Para que los datos no se coloquen simultáneamente en el bus, existe un "arbitraje" que determina cuál de las señales tiene prioridad en el envío de los datos.

Características Eléctricas

Tanto las líneas SDA como SCL son bidireccionales y deben estar conectadas al positivo de la alimentación a través de una fuente de alimentación o un resistor pull-up, consulte la figura 5.

Cuando el bus está libre, ambas líneas permanecen en el nivel alto. Los dispositivos conectados al bus deben tener un drenaje o un colector abiertos para formar una función AND. Los datos se transfieren a una velocidad de 100 kbits/s o 400 kbits/s en modo Estándar o 3,4 Mbits/s en modo High Speed.

El número de interfaces conectadas al bus dependerá únicamente de la capacidad del bus de acuerdo con lo que se indica en la parte inicial.

Debido a que hay dispositivos de una amplia variedad de tecnologías que se pueden conectar al bus, los niveles bajos y altos (0 y 1) no son fijos y dependen solamente del nivel asociado de Vdd. Cada pulso del clock se transfiere un poco de datos.

Para que los datos transferidos sean válidos, la fila SDA debe permanecer estable durante el período en el que el clock permanece en el nivel alto.

Los niveles de fila de datos altos o bajos pueden cambiar solamente cuando la señal de clock en la línea SCL está en el nivel bajo, tal y como se muestra en

el diagrama de tiempo en la figura 6.

En la figura 7 tenemos otro diagrama de tiempo que muestra las condiciones START y STOP.

Dentro de la operación del bus I2C tenemos los procedimientos START y STOP (S y P). Una transición del nivel alto para el bajo en la línea SDA mientras que la línea SCL está en el nivel alto, es un solo caso que puede ocurrir indicando una situación de START.

Una transición de nivel bajo a alto en la línea SDA mientras que la línea SCL permanece en el nivel alto define una condición STOP. Estas condiciones siempre las genera el maestro. El bus se considera ocupado después de una condición START, y libre de nuevo algún tiempo después de la condición STOP

Si se generan condiciones START, el bus permanecerá ocupado. Con los circuitos adecuados puede implementar la función de detectar las condiciones START y STOP en los dispositivos que deben estar conectados al bus.

EL FORMATO DEL BYTE

Cada byte colocado en la línea SDA debe tener 8 bits de largo. El número de bytes que se pueden transferir en cada operación de transferencia es ilimitado.

Cada byte solo tiene que ir seguido de un bit de reconocimiento, los bytes se transfieren de modo que el bit MSB más significativo vaya primero.

Si el dispositivo que recibe la señal no puede manejar los datos recibidos, puede cambiar la línea SCL colocándola en el nivel bajo para forzar al maestro a entrar en un estado de espera.

Sólo cuando la línea esté libre de nuevo, la transferencia de datos podrá continuar

RECONOCIMIENTO

El reconocimiento de los datos transferidos es obligatorio. El pulso generado para este propósito se muestra en la figura 8.

El receptor tiene la línea SDA colocada en el nivel bajo durante el pulso del clock para que permanezca estable en el nivel bajo durante el período alto del pulso de clock.

GENERACIÓN DE CLOCK Y ARBITRAJE

Porque todas las unidades maestras generan sus propias señales de clock, en la línea SCL existe el peligro de que estos pulsos afecten a la transferencia de mensajes si se mezclan. Para evitar esto, los datos se validan solamente en el período en el que la señal de clock está en el nivel alto. Esto significa la necesidad de tener un arbitraje bit a bit.

La sincronización de los clocks se hace a través de los puertos AND en las interfaces de bus. En ellos, una transición del nivel alto al bajo en la línea SCL hará que la cuenta comience en el período bajo, y una vez que un clock de un dispositivo tenga ido al nivel bajo, mantendrá la línea SCL en ese estado hasta que se alcance un nivel de alto del clock, sea alcanzado, observe la figura 9.

Figura 9 - Sincronización durante el arbitraje

Sin embargo, la transición del bajo al nivel alto en este clock no causará un cambio de estado en la línea SCL si otro clock todavía está en el período de bajo nivel. La línea SCL se mantendrá en el nivel bajo por el dispositivo que tiene el período más largo en el nivel bajo.

Los dispositivos con períodos más cortos en el nivel bajo entrarán en un estado de espera en el nivel alto durante ese tiempo. Cuando todos los dispositivos han contado su tiempo en el nivel bajo, el clock será liberado y llegará al nivel alto.

Esto no ocurrirá entre los clocks del dispositivo y el estado de la línea SCL, y todos los dispositivos reanudarán el conteo de sus períodos en el nivel alto. El primer dispositivo que complete su tiempo en el nivel alto volverá a colocar la línea SCL en el nivel bajo.

De esta manera, un clock SCL sincronizado se puede generar a través de este período bajo, determinado por el dispositivo que tiene el período en el nivel bajo más largo y su período en el nivel alto será determinado por el menor tiempo en esta situación.

Un maestro debe comenzar a transferir datos solo si el bus es libre. Dos o más maestros deben generar una condición START, con el tiempo máximo de manutención de la condición START dando como resultado una condición START definida en el bus.

El arbitraje tendrá lugar en la línea SDL en el instante en que la línea SCL esté en el nivel alto de tal manera que un maestro transmita el alto nivel, mientras que el que tiene la transmisión en el nivel bajo está apagado. El arbitraje puede continuar durante varios bits.

Su primera etapa es la comparación de los bits de direccionamiento. Si los maestros intentan abordar el mismo dispositivo, el arbitraje continúa comparando los bits de datos verificando si se transmiten o los bits de reconocimiento.

La figura 10 muestra las formas de señales que se producen en el proceso de arbitraje que determina cuál de las transmisiones prevalecerá en una transmisión de datos.

Tenga en cuenta que debido a que en este tipo de bus el control se decide sólo en los códigos de direccionamiento maestro y los datos enviados por los maestros, no hay ningún maestro central o ninguna orden de prioridad en el bus.

Un punto importante al que se debe llamar la atención surge durante una transferencia de datos cuando el procedimiento de arbitraje todavía se está produciendo cuando se transmite una condición START o STOP al bus.

Si tal situación sucede, los maestros deben enviar esta condición START o STOP en la misma posición y formato.

FORMATOS DE DATOS

Hay varias posibilidades para la transmisión de datos. Vea a continuación:

a) En un primer formato, el transmisor maestro envía las señales a un receptor esclavo. Las señales no tienen el significado de su flujo modificado. Es la forma más sencilla de transferir datos. Como se ilustra en la figura 11.

b) En una segunda posibilidad, el maestro hace una lectura del esclavo inmediatamente después de la primera bit. En el momento del primer reconocimiento, el transmisor maestro se convierte en un receptor maestro y el receptor esclavo se convierte en un transmisor esclavo. El primer reconocimiento sigue siendo generado por el esclavo. La condición STOP es generada por el maestro, que debe haber enviado previamente una señal de no reconocimiento.

b) Un formato combinado se muestra en la figura 12.

Durante un cambio de dirección del flujo de señal, con una transferencia se repiten la condición START y la dirección del esclavo, pero con el bit R/N invertido.

Si un receptor maestro envía una condición START repetidamente, debe haber enviado previamente una condición de no reconocimiento.

Es importante tener en cuenta que se pueden utilizar formatos combinados y que todas las decisiones sobre el incremento automático o la disminución de las concesiones de memoria a las que se accede además de otras características del sistema deben ser tomadas por el proyectista del dispositivo.