Describimos el proyecto de un divisor programable de frecuencia digital (CMOS), que puede hacer la división por valores enteros continuamente en el rango de l a 9999, con la posibilidad de expansión por la simple repetición de los módulos. Las aplicaciones en laboratorio, en industria y recreativas serán sugeridas en el transcurso del artículo.

Este divisor programable de frecuencia utiliza circuitos integrados digitales CMOS y puede hacer divisiones por cualquier valor entero entre 1 y 9999.

Se utilizan llaves digitales programables que permiten la selección de los valores de la división con facilidad, lo que lleva a innumerables posibilidades de aplicaciones prácticas.

Entre estas aplicaciones sugerimos las siguientes:

Cuenta programada de objetos en una línea de montaje automatizada, con la parada, accionamiento de alarmas cuando el valor deseado es alcanzado.

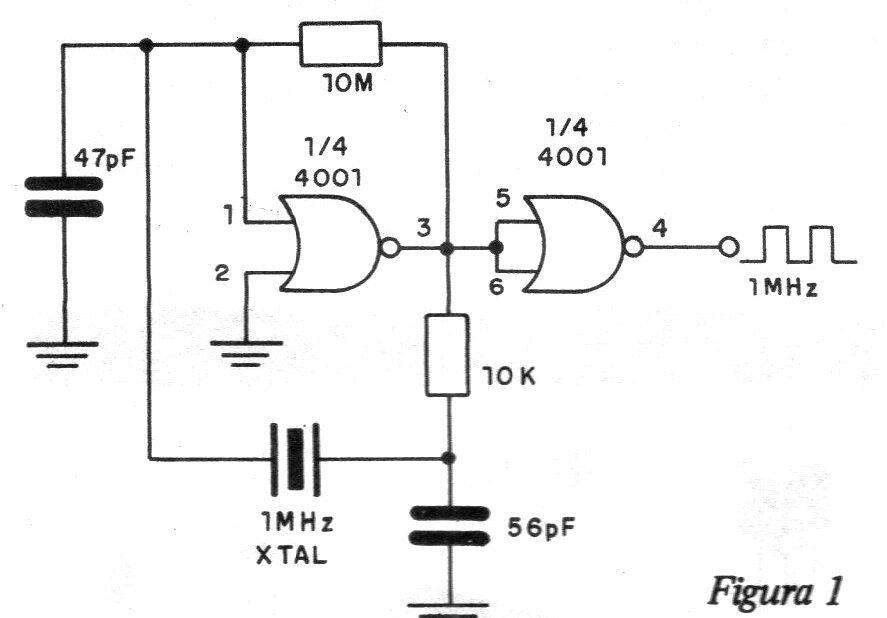

La conexión de un oscilador de 1MHz (como muestra la figura 1) en la entrada permite hacer un generador de frecuencias, que producirá señales en el rango que va de 1MHz / 9999 hasta 1MHz / 1, lo que significa algo como 100 Hz hasta 1 MHz .

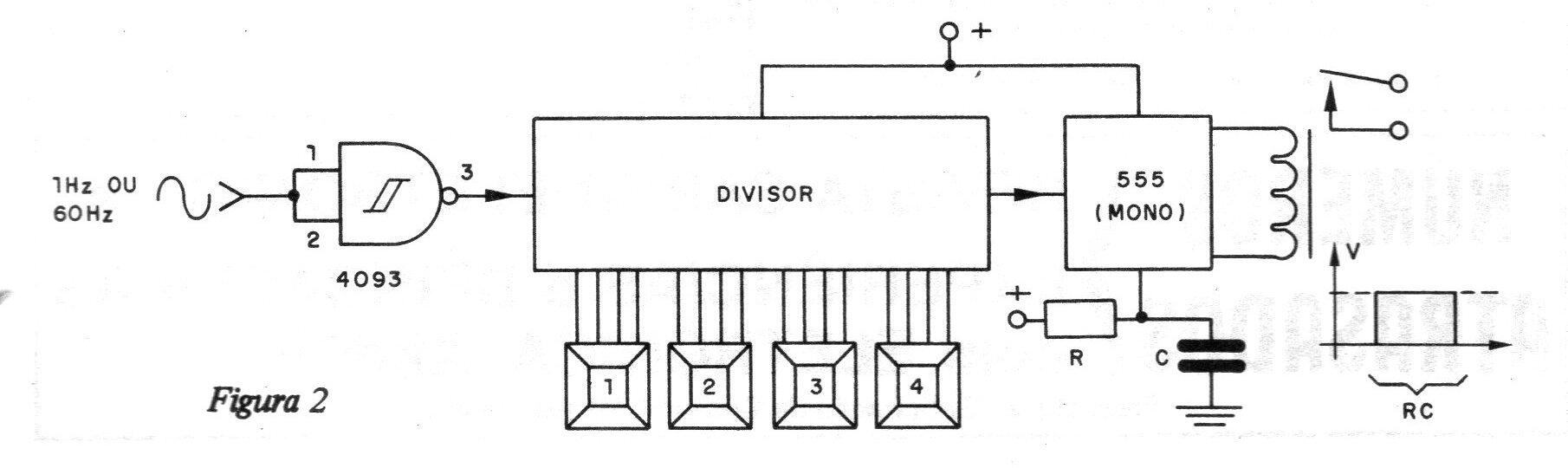

Excitando con una señal de baja frecuencia (1 Hz o 60 Hz) podemos hacer un temporizador de precisión, como sugiere la figura 2.

Este temporizador puede generar pulsos en intervalos de 9999/1 en el caso de un estándar de 1Hz o 9999/60 -166 segundos, en el caso de un estándar de 60 Hz.

Otras aplicaciones pueden ser fácilmente imaginadas por los lectores.

Como funciona

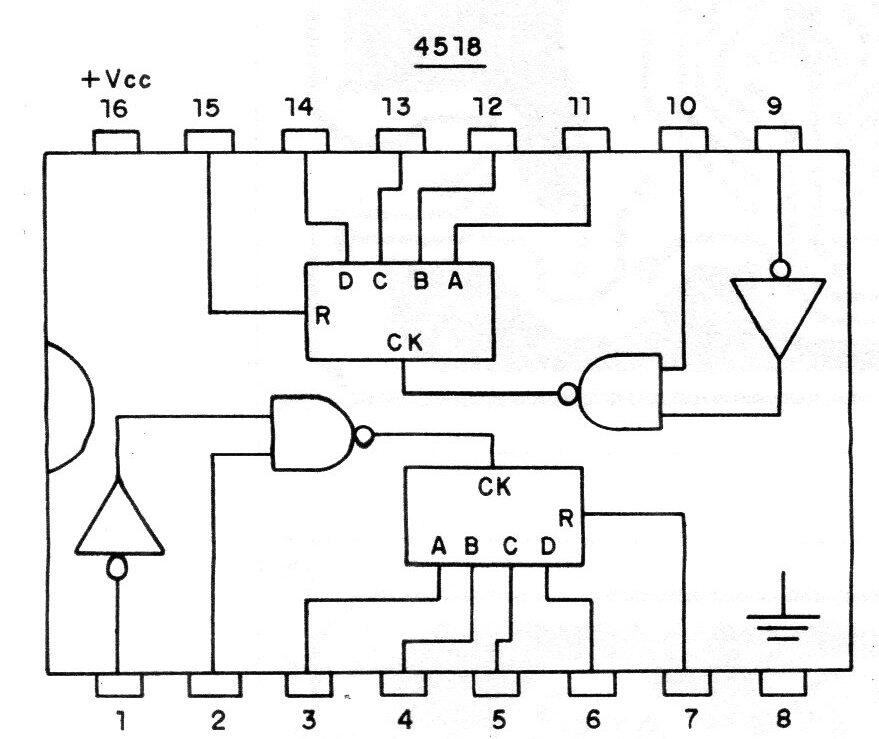

La base del circuito es el "Dual Synchronous Divide by-10 Counter" o traduciendo, un divisor doble síncrono por 10, del tipo CMOS, cuyo aspecto y el circuito interno se muestran en la figura 3.

Como podemos percibir este integrado contiene dos divisores por 10 que pueden ser programados para dividir la frecuencia por valores entre 1 y 9.

La programación se realiza por las propias salidas que siguen la codificación BCD, a través de una llave.

Usando dos integrados de este tipo en cascada podemos hacer la división por 9999, ya que cada uno contiene dos divisores que nos suministran dos dígitos (99) en la división máxima.

Con el aumento de un tercer integrado podemos tener otros dos dígitos, lo que nos lleva a la división por valores hasta 999999.

Los integrados CMOS utilizados en este circuito divisor pueden trabajar con frecuencias de hasta 6 MHz (con alimentación de 10 V) o 2,5 MHz (con alimentación de 5 V).

En la operación con frecuencias elevadas se recomienda que el pasador 16 del integrado (alimentación) quede lo más cerca posible del capacitor de filtro de la fuente, y que sea desacoplado con la conexión de capacitores de 100 nF (104) cerámicos.

Estos capacitores se conectarán junto a los propios pines 16 de los integrados.

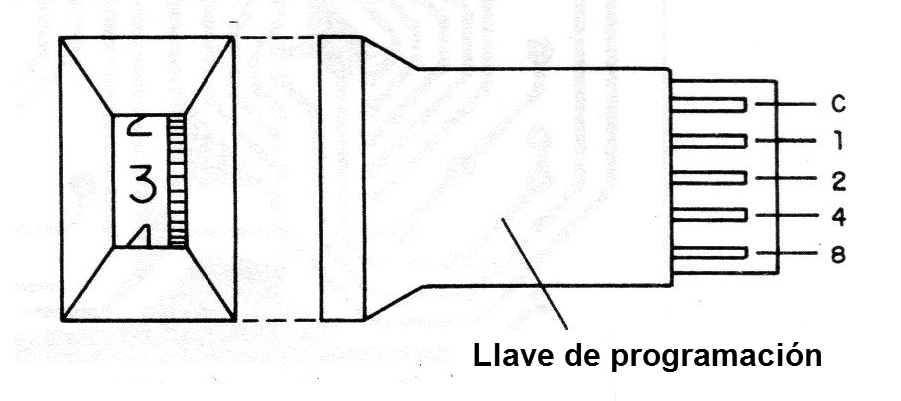

Observe que la programación se realiza con una llave de 10 posiciones BCD que tiene 5 terminales comunes más las salidas codificadas como muestra la figura 4.

La tensión de alimentación del circuito puede variar entre 5 y 15 V.

Montaje

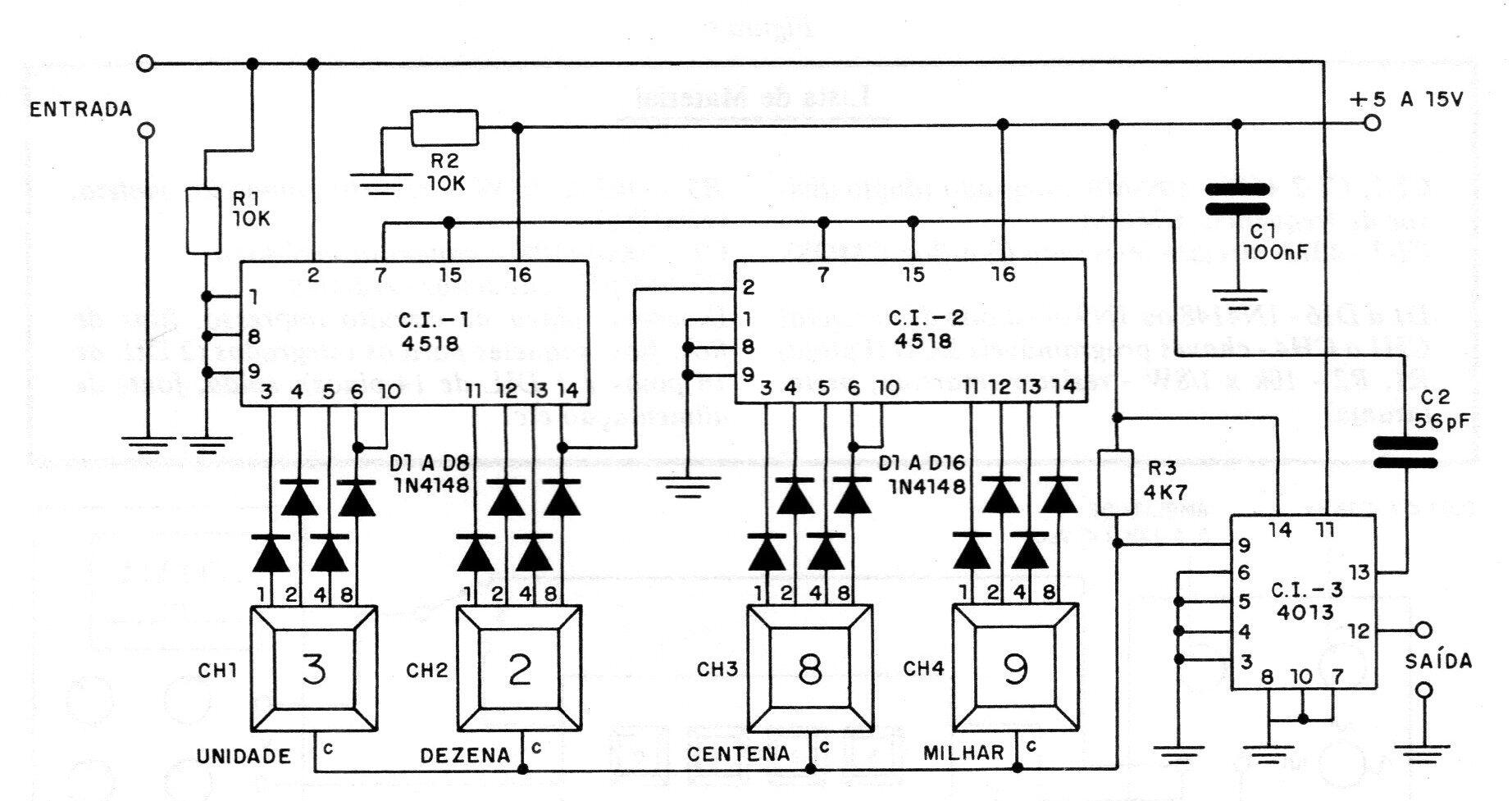

El diagrama completo del divisor se muestra en la figura 5.

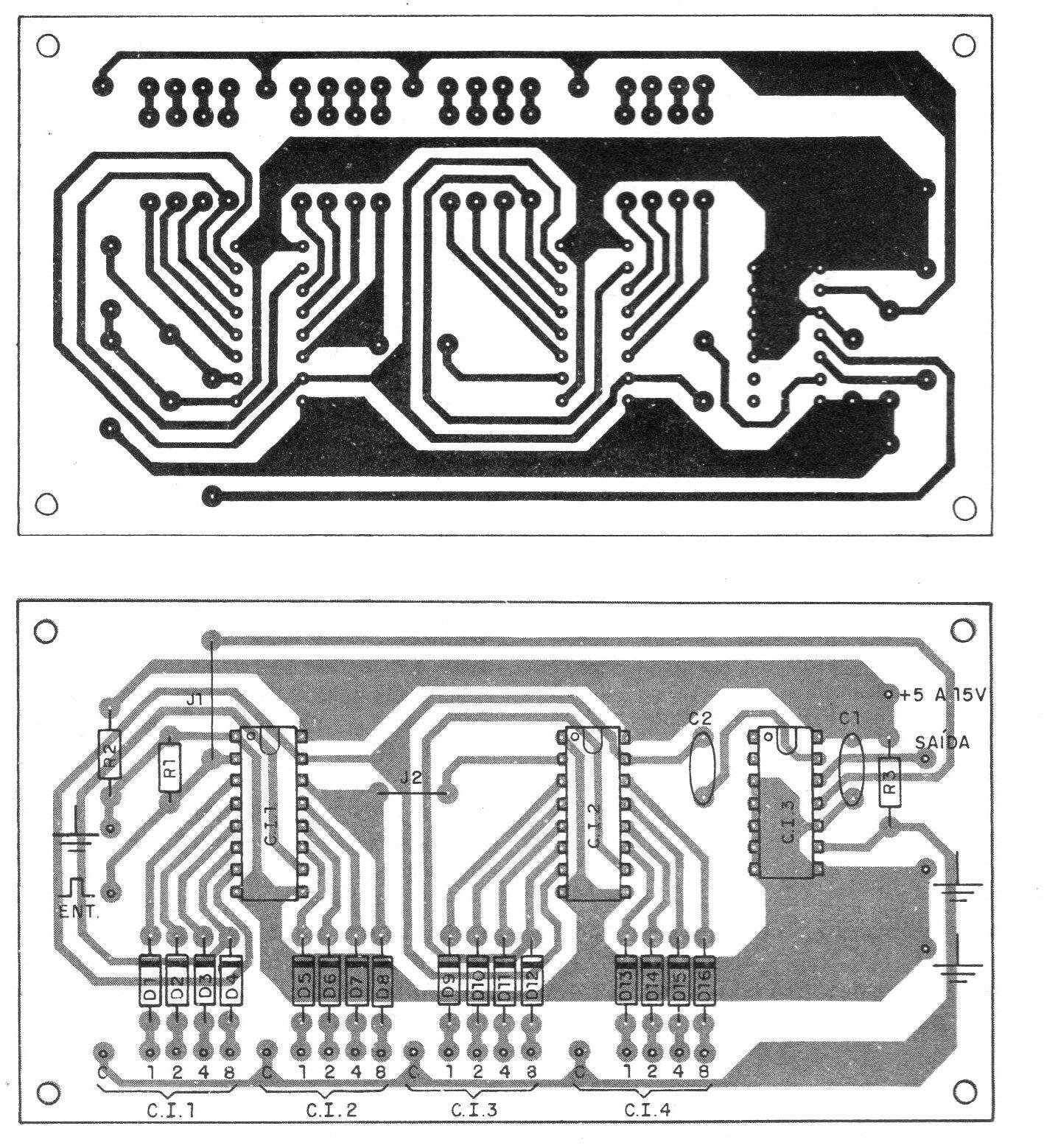

En la figura 6 tenemos nuestra sugerencia de placa de circuito impreso.

Además de los cuidados normales con el trato de los componentes, observación de polaridades, recomendamos que:

- La fuente utilizada se estabiliza. Las conexiones de las llaves programadoras deben realizarse con hilos cortos.

- El montador debe estar atento a la identificación de los hilos de conexión de las llaves para que la codificación sea seguida en la división.

Las señales de excitación deben ser compatibles con las características de los integrados digitales CMOS.

Prueba

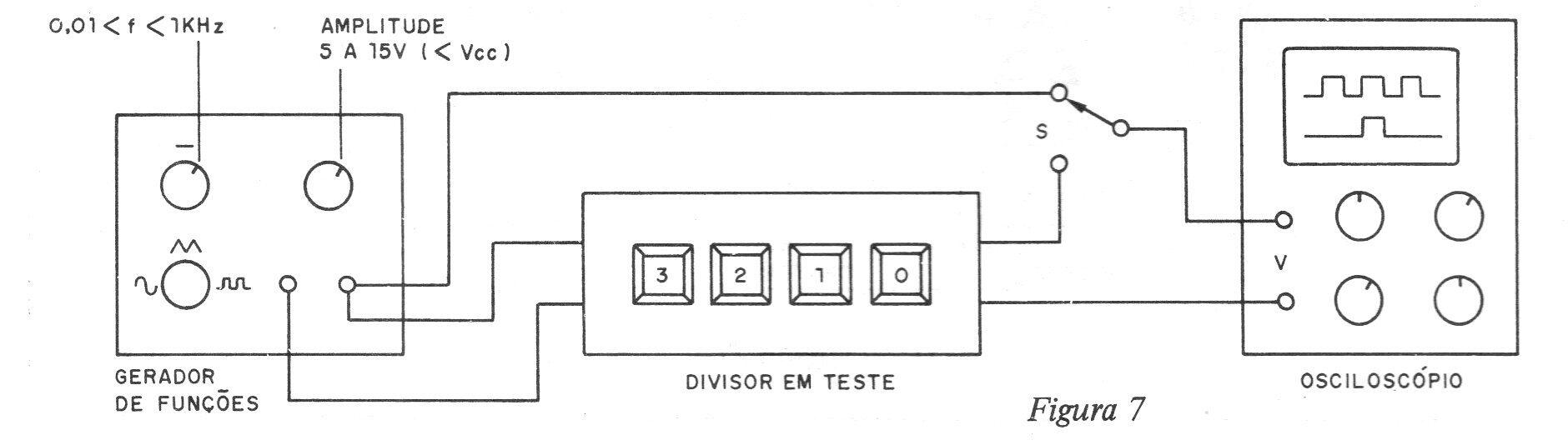

La prueba puede realizarse con ayuda de un osciloscopio y un generador de funciones, conforme la conexión mostrada en la figura 7.

Elegir valores enteros de frecuencia para el generador y para el divisor podemos tener un control más fácil del funcionamiento.

La frecuencia producida en el generador y dividida puede entonces visualizarse en el osciloscopio.

CI-1, CI-2 4518 - circuito integrado (doble divisor de frecuencia CMOS)

CI-3 - 4013- circuito integrado (flip-flop CMOS)

D1 a D16 - 1N4148 o 1N914 - diodo de uso general

CH1 a CH4 - llaves programables BCD (Patola)

R1, R2 - 10 k x 1/8 W - resistor (marrón, negro, naranja)

R3 - 4k7 x 1/8 W - resistencia (amarillo, violeta, rojo)

C1 - 100 nF (104) - capacitor de cerámica

C2 - 56 pF - capacitor de cerámica

Varios: placa de circuito impreso: cintas de hilos, hilos, sockets para los integrados (2 DIL de 16 pines y 1 DIL de 14 pines), soldadura, fuente de alimentación, etc.