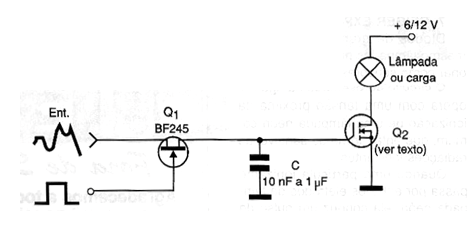

La altísima resistencia de entrada de un Power-FET posibilita la elaboración de un circuito de muestreo y retención para señales analógicas, bastante simples. En la figura tenemos el circuito básico para esta aplicación que funciona de la siguiente manera. Cuando el FET de unión (Q1) está habilitado, la señal a ser muestreada carga el capacitor C con la tensión que presenta en ese instante. Una vez deshabilitado, la tensión en el condensador se puede mantener durante un buen tiempo hasta el siguiente muestreo. Esta tensión de muestreo que está en el condensador determina la conducción del transistor de efecto de campo de potencia y, por lo tanto, la corriente en la carga.